# **Chapter-2**

DecoderEncoderMUX

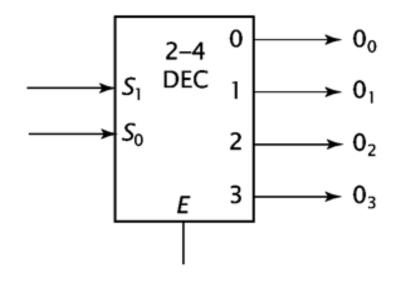

#### Accepts a value and decodes it

Output corresponds to value of *n* inputs

#### Consists of:

- Inputs (n)

- Outputs ( $2^n$  , numbered from  $0 \rightarrow 2^n$  1)

- Selectors / Enable (active high or active low)

# The truth table of 2-to-4 Decoder

| <i>S</i> <sub>1</sub> | <i>S</i> <sub>0</sub>                   | Ε | 00 | 01 | 02 | 03 |

|-----------------------|-----------------------------------------|---|----|----|----|----|

| Х                     | х                                       | 0 | 0  | 0  | 0  | 0  |

| 0                     | S <sub>0</sub><br>X<br>0<br>1<br>0<br>1 | 1 | 1  | 0  | 0  | 0  |

| 0                     | 1                                       | 1 | 0  | 1  | 0  | 0  |

| 1                     | 0                                       | 1 | 0  | 0  | 1  | 0  |

| 1                     | 1                                       | 1 | 0  | 0  | 0  | 1  |

| <i>S</i> <sub>1</sub> | <i>S</i> <sub>0</sub>               | Ε | 00 | 01 | 02 | 03 |

|-----------------------|-------------------------------------|---|----|----|----|----|

| х                     | х                                   | 0 | 0  | 0  | 0  | 0  |

| 0                     | <i>S</i> ₀<br>X<br>0<br>1<br>0<br>1 | 1 | 1  | 0  | 0  | 0  |

| 0                     | 1                                   | 1 | 0  | 1  | 0  | 0  |

| 1                     | 0                                   | 1 | 0  | 0  | 1  | 0  |

| 1                     | 1                                   | 1 | 0  | 0  | 0  | 1  |

(b)

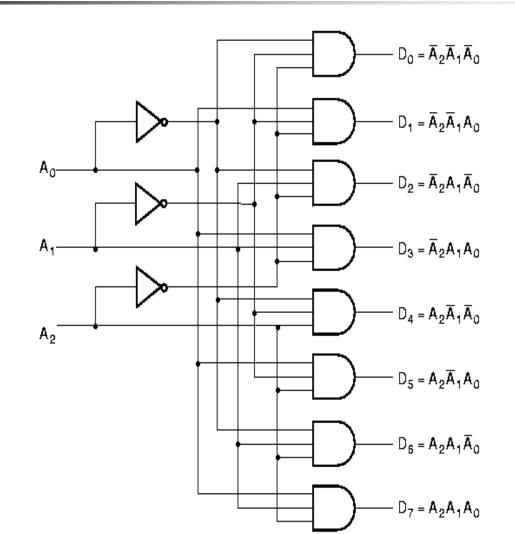

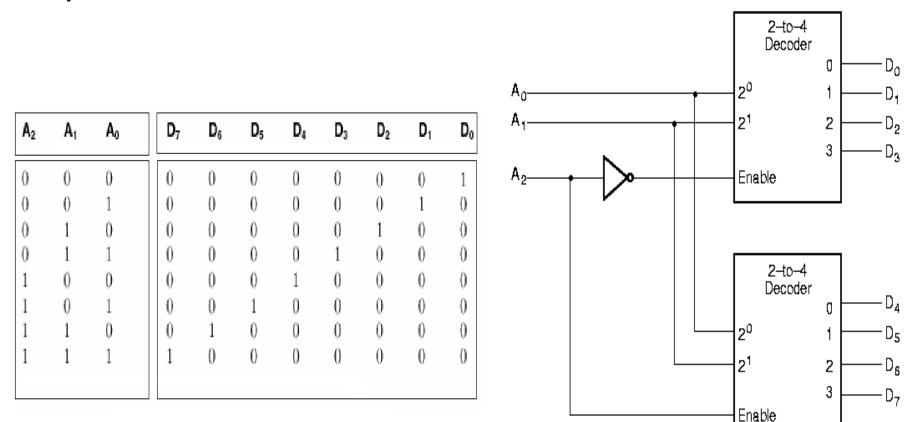

# The truth table of 3-to-8 Decoder (Remaining values in truth table will be Zeroes)

| A2 | A1 | A0 | <b>D0</b> | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

|----|----|----|-----------|----|----|----|----|----|----|----|

| 0  | 0  | 0  | 1         |    |    |    |    |    |    |    |

| 0  | 0  | 1  |           | 1  |    |    |    |    |    |    |

| 0  | 1  | 0  |           |    | 1  |    |    |    |    |    |

| 0  | 1  | 1  |           |    |    | 1  |    |    |    |    |

| 1  | 0  | 0  |           |    |    |    | 1  |    |    |    |

| 1  | 0  | 1  |           |    |    |    |    | 1  |    |    |

| 1  | 1  | 0  |           |    |    |    |    |    | 1  |    |

| 1  | 1  | 1  |           |    |    |    |    |    |    | 1  |

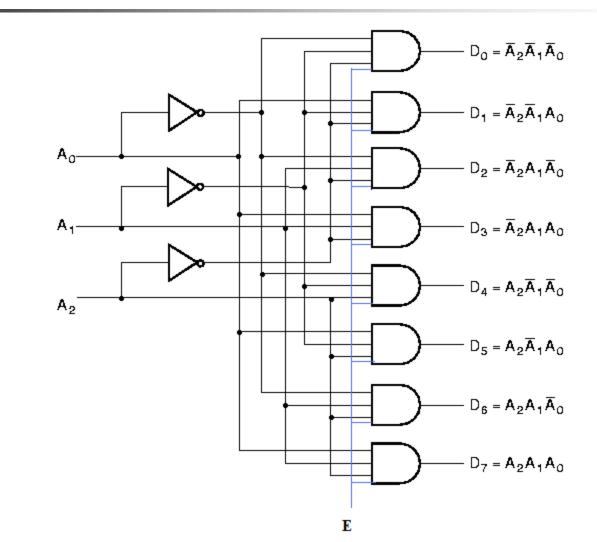

# 3-to-8 Decoder

# 3-to-8 Decoder with Enable

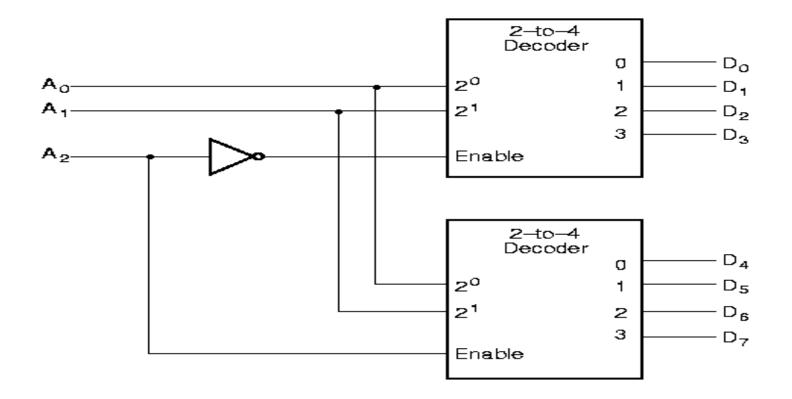

### **Decoder Expansion**

- Decoder expansion

- Combine two or more small decoders with enable inputs to form a larger decoder

- 3-to-8-line decoder constructed from two 2-to-4-line decoders

- The (Most Significant Bit) MSB is connected to the enable inputs

- if A<sub>2</sub>=0, upper is enabled; if A<sub>2</sub>=1, lower is enabled.

### **Decoder Expansion**

# Combining two 2-4 decoders to form one 3-8 decoder using enable switch

The highest bit is used for the enable

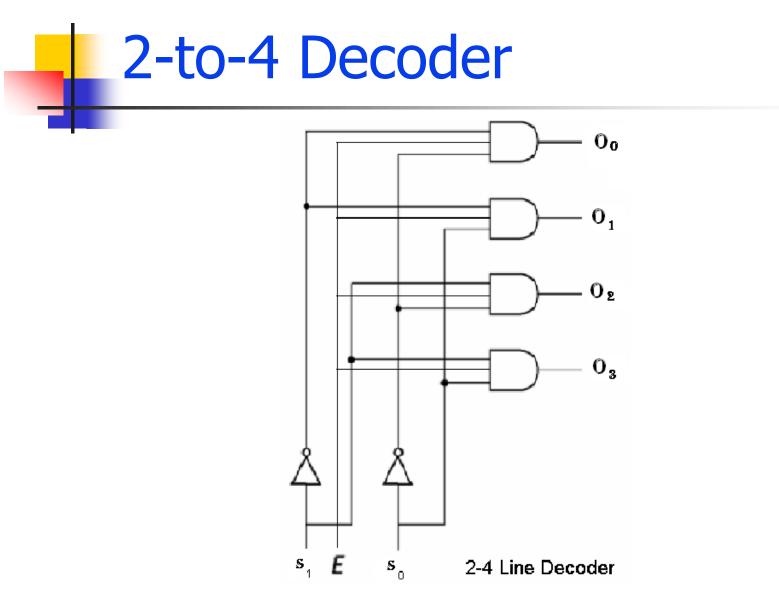

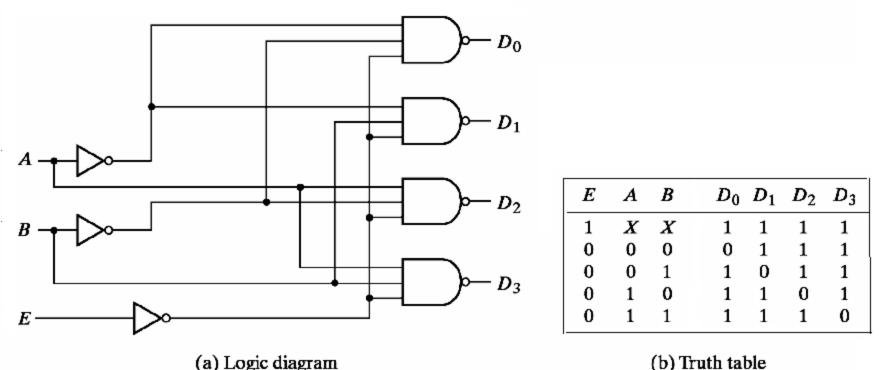

# 2-to-4 Decoder: NAND implementation

Decoder is enabled when E=0 and an output is active if it is 0

2-to-4-Line Decoder with Enable Input

- Decoder

- Encoder

- Mux

- Perform the inverse operation of a decoder

- 2<sup>n</sup> (or less) input lines and n output lines

Perform the inverse operation of a decoder

2<sup>n</sup> (or less) input lines and n output lines

#### **Table: Truth Table for Octal-to-Binary**

| D <sub>7</sub> | D <sub>6</sub> | $D_5$ | D₄ | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | <b>A</b> 2 | <b>A</b> <sub>1</sub> | <b>A</b> 0 |

|----------------|----------------|-------|----|----------------|----------------|----------------|----------------|------------|-----------------------|------------|

| 0              | 0              | 0     | 0  | ٥              | 0              | 0              | 1              | 0          | 0                     | ٥          |

| 0              | 0              | 0     | 0  | 0              | 0              | 1              | 0              | 0          | 0                     | 1          |

| 0              | 0              | 0     | 0  | 0              | 1              | 0              | 0              | 0          | 1                     | 0          |

| 0              | 0              | 0     | 0  | 1              | 0              | 0              | 0              | 0          | 1                     | 1          |

| 0              | 0              | 0     | 1  | 0              | 0              | 0              | 0              | 1          | 0                     | 0          |

| 0              | 0              | 1     | 0  | 0              | 0              | 0              | 0              | 1          | 0                     | 1          |

| 0              | 1              | 0     | 0  | 0              | 0              | 0              | 0              | 1          | 1                     | 0          |

| 1              | 0              | 0     | 0  | 0              | 0              | 0              | 0              | 1          | 1                     | 1          |

|                |                |       |    |                |                |                |                |            |                       |            |

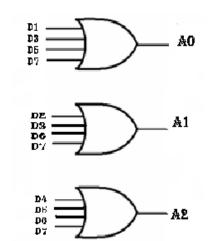

#### Encoders

Encoders can be implemented with OR gates whose inputs are determined directly from the truth table. Output Ao=1 if the input octal digit is 1 or 3 or5 or 7. Similar conditions apply for the other two outputs. These can be expresses by the following Boolean functions with 3 OR gates

$$A_0 = D_1 + D_3 + D_5 + D_7;$$

$$A_1 = D_2 + D_3 + D_6 + D_7;$$

$$A_2 = D_4 + D_5 + D_6 + D_7;$$

- Decoder

- Encoder

- Mux

# Multiplexer (MUX)

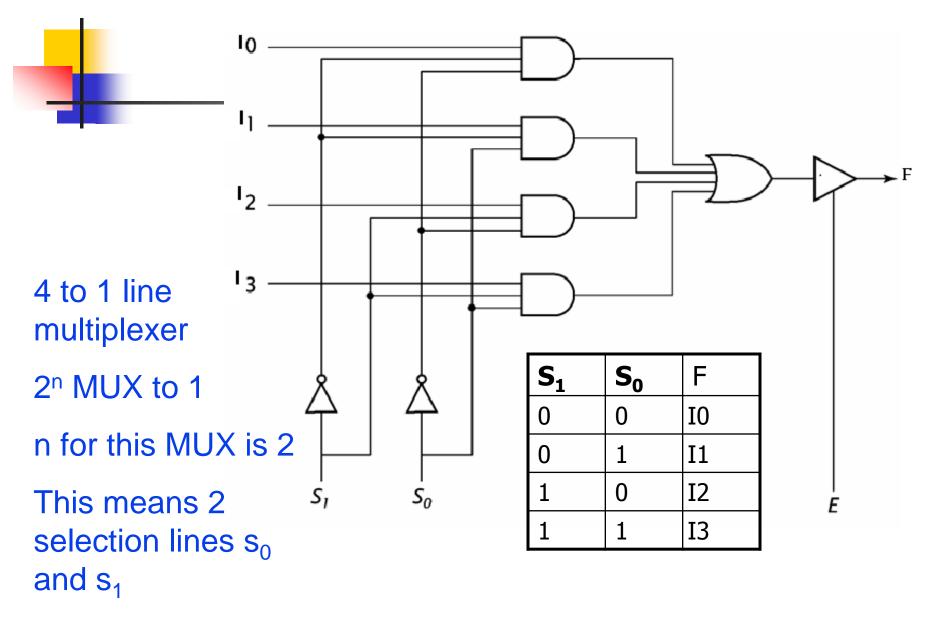

A multiplexer can use addressing bits to select one of several input bits to be the output.

- A selector chooses a single data input and passes it to the MUX output

- It has one output selected at a time.

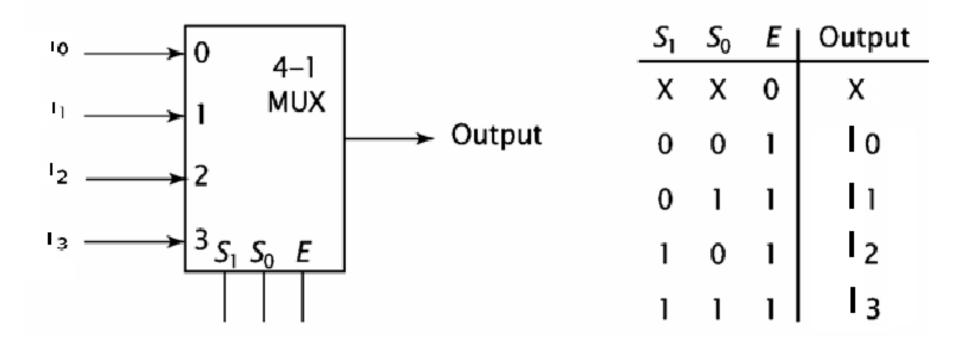

#### Function table with enable

#### 4 to 1 line multiplexer

# Multiplexer (MUX)

Consists of:

- Inputs (multiple) = 2<sup>n</sup>

- Output (single)

- Selectors (# depends on # of inputs) = n

- Enable (active high or active low)

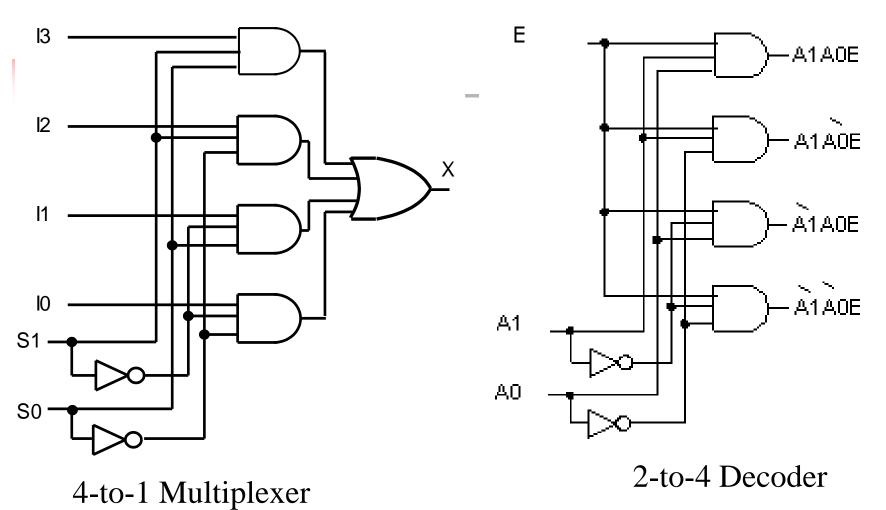

# Multiplexers versus decoders

• A <u>Multiplexer</u> uses n binary select bits to choose from a maximum of  $2^n$  unique input lines.

•Decoders have 2^n number of output lines while multiplexers have only <u>one output line</u>.

•The output of the multiplexer is the data input whose index is specified by the *n* bit code.

## **Multiplexer Versus Decoder**

Note that the multiplexer has an extra OR gate. A1 and A0 are the two inputs in decoder. There are four inputs plus two selecs in multiplexer.

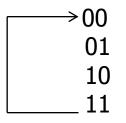

Binary Counter (example of sequential circuit): A register that goes through a predetermined sequence of states upon the application of input pulses is called a counter. They may occur at uniform intervals of time. They are used for counting no. of occurrences of an event A counter that follows the binary number sequence is called a binary counter. There are two types of counters: Binary up counter and Binary down counter. 2-bit binary up counter generates values iteratively in ascending order e.g.

while 2-bit binary down counter generates values in descending order e.g. 11, 10, 01, 00

A register is a storage location located inside the processor. A modern processor has many registers.

Registers are used to hold :

1. Registers

- data which is being processed

- instructions which are being executed

- addresses which are about to be accessed.

Register

Register

- A common sequential device: Registers

- They're a good example of sequential analysis and design

- They are also frequently used in building larger sequential circuits

- Registers hold larger quantities of data than individual flip-flops

- Registers are central to the design of modern processors

- There are many different kinds of registers

- We'll show some applications of these special registers

#### What good are registers?

- Flip-flops are limited because they can store only one bit

- A register is an extension of a flip-flop that can store multiple bits

- Registers are commonly used as temporary storage in a processor

- They are faster and more convenient than main memory

- More registers can help speed up complex calculations

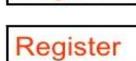

#### A basic register

- Basic registers are easy to build. We can store multiple bits just by putting a bunch of flip-flops together!

- A 4-bit register is given below

- This register uses D flip-flops, so it's easy to store data without worrying about flip-flop input equations

- All the flip-flops share a common CLK and CLR signal

- With each rising edge of clock pulse data is inputted as Do, D1, D2 and D3 and as D-flip-flop is used so finally same values are retained in flipflops so as to be generated as final output values of Qo,Q1,Q2 and Q3

- Clear input is used for clearing all values of register 0's before clock operation

29

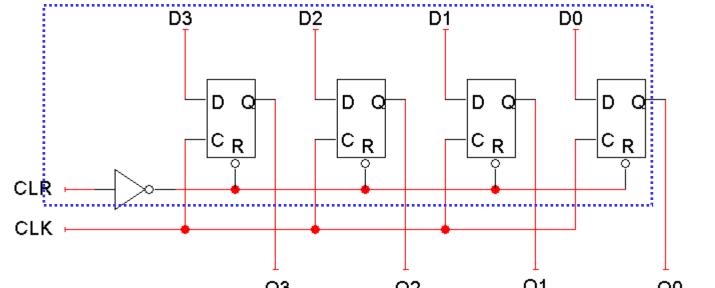

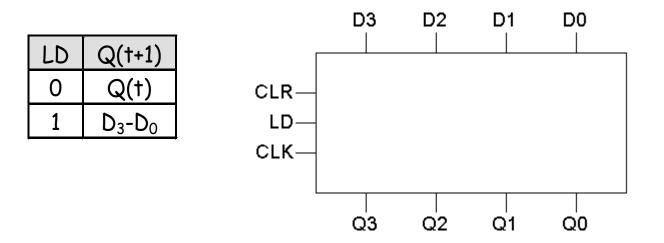

#### Adding a parallel load operation

- Tranfer of new information into a registe ris referred to as loading a register

- The input  $D_3$ - $D_0$  is copied to the output  $Q_3$ - $Q_0$  on every clock cycle

- How can we store the current value for more than one cycle?

- Let's add a load input signal LD to the register

- If LD = 0, the register keeps its current contents

- If LD = 1, the register stores a new value, taken from inputs  $D_3-D_0$

Random Access Memory. This is where information is stored temporarily while the computer is on although this is lost when the computer is switched off!

Read Only Memory. This is where data and programs are stored permanently.

#### **MEMORY CLASSIFICATION**

In general the memory is classified in two types based on their mode of access of a memory system.

- 1. Random access memory

- 2. Sequential access memory

- **<u>Random Access Memory</u>**: The world of data reading or writing from or to the memory requires same time. We can access the data randomly.

Example: hard disk.

#### Types of ROM

#### • PROM - Programmable Read Only Memory:

Creating ROM chips totally from scratch is time-consuming and very expensive in small quantities. For this reason, developers created a type of ROM known as programmable read-only memory (PROM). Blank PROM chips can be bought inexpensively and coded by the user with a programmer. PROM chips have a grid of columns and rows just as ordinary ROMs do. It can be programmed using electrical fuses

#### EPROM - Erasable Programmable Read Only Memory

Working with ROMs and PROMs can be a wasteful business. Even though they are inexpensive per chip, the cost can add up over time. Erasable programmable read-only memory (EPROM) addresses this issue. EPROM chips can be rewritten many times. Erasing an EPROM requires a special tool that emits a certain frequency of ultraviolet (UV) light.

#### • EEPROM - Electrically Erasable Programmable Read Only Memory

• Though EPROMs are a big step up from PROMs in terms of reusability, they still require dedicated equipment and a laborintensive process to remove and reinstall them each time a change is necessary. Also, changes cannot be made incrementally to an EPROM; the whole chip must be erased. Electrically erasable programmable read-only memory (EEPROM) chips remove the biggest drawbacks of EPROMs.

In EEPROMs:

- The chip does not have to removed to be rewritten.

- The entire chip does not have to be completely erased to change a specific portion of it.

- Changing the contents does not require additional dedicated equipment.